大家好,今天小编关注到一个比较有意思的话题,就是关于verilog计数器是什么的问题,于是小编就整理了4个相关介绍的解答,让我们一起看看吧。

verilog hdl如何实现计分器?

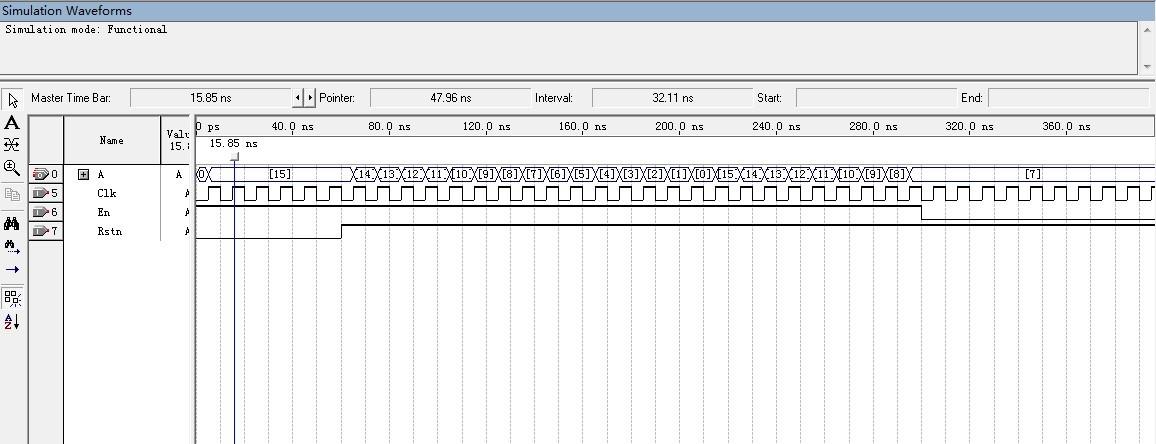

在Verilog HDL中实现计分器可以使用一个计数器模块和一个显示模块。计数器模块可以使用寄存器来存储计数值,并通过时钟信号进行递增。

显示模块可以将计数值转换为对应的显示格式,并输出到数码管或其他显示设备上。

通过将计数器模块和显示模块连接起来,可以实现一个完整的计分器。可以根据需求添加其他功能,如重置按钮、暂停功能等。

以4分频作为一个例子 两比特计数器计数,在每个输入时钟的上升沿计数器加1 这样计数器会计数 0 -》1 -》2-》3-》0 表达为二进制为: 00 01 10 11 可以看到计数器的高位每四个输入时钟的变化是 0,0,1,1。 因此如果把计数器的高位作为一个输出时钟,它每四个输入时钟的周期完成一次0011的周期。 因此相对于输入时钟实现了4分频

6分频是什么意思?

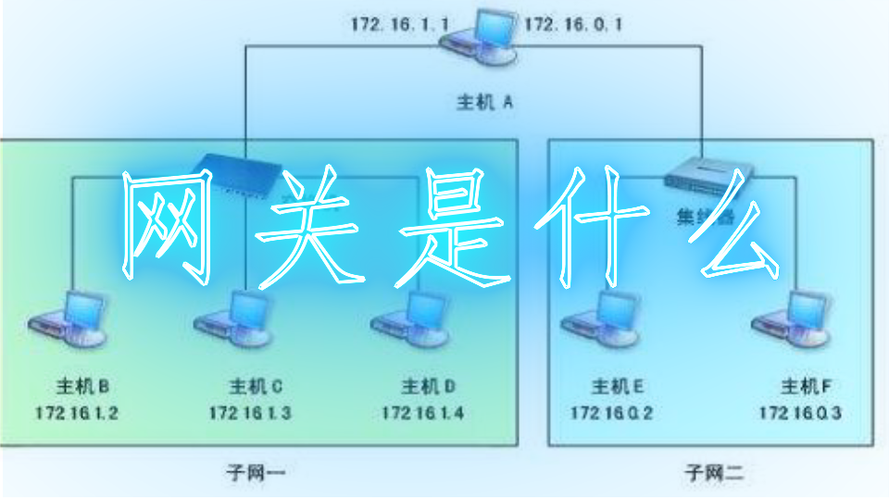

6分频的意思是:用系统时钟6分频后作为计数脉冲。如果系统时钟是12MHz的话,计数脉冲就是2MHz。

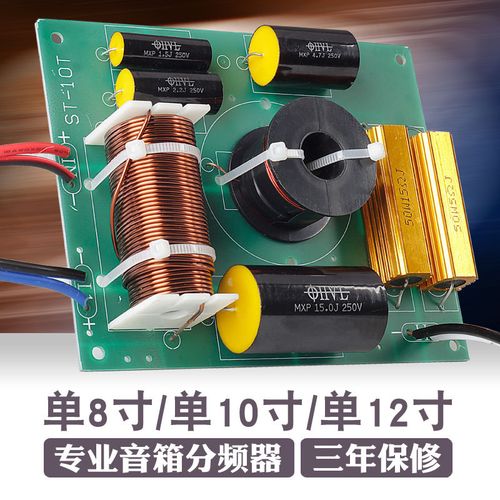

分频器:

1.定义

分频器是数字系统设计中最常见的基本电路之一。所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。

分频器分为偶数分频器和奇数分频器,和计数器非常类似,有时候甚至可以说就是一个东西。

2.实现分频

想得到比固定时钟频率更慢的时钟,可以将固定时钟进行分频,想得到比固定时钟频率更快的时钟,可以将固定时钟进行倍频又两种方式实现分频与倍频,①锁相环pll、②自己编写verilog语言来实现。

3.奇偶分频

偶分频:成倍数低于输入频率的输出信号有2、4、6、8分频。奇分频:成倍数低于输入频率的输出信号有3、5、7、9分频。分频就是输出信号的一个周期对应clk的6个周期,

凡是时钟信号都要连接到全局时钟网络,也叫全局时钟数,它是FPGA厂家专为时钟路径而特殊设计的,它能使时钟信号到达每个寄存器的时间都尽可能相同。更容易在高速系统中保持信号稳定。

就是说用系统时钟6分频后作为计数脉冲。如果系统时钟是12MHz的话,计数脉冲就是2MHz。

fpga是什么意思?

FPGA全称叫做Field-Programmable Gate Array, 中文全称叫做现场可编程门阵列。

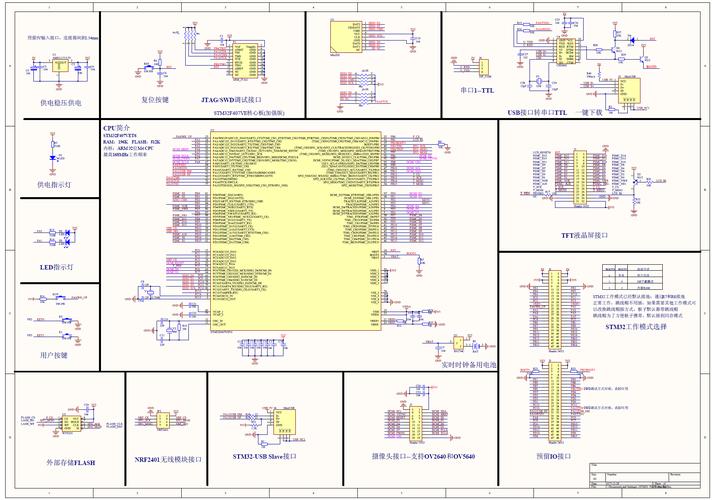

FPGA是一种可编程芯片,可以在其上实现数字电路设计。比如,我们设计了一个计数器,我们可以先用Verilog HDL语言对计数器进行描述,然后通过FPGA编译器(比如Intel Quartus, Xilinx Vivado)将计数器转换成配置码流,接着将码流下载到FPGA芯片上,此时,这个FPGA芯片就相当于一个专门用于计数的芯片了。

八进制时钟脉冲计数器参考资料?

关于八进制时钟脉冲计数器的参考资料,可以在相关的电子书籍或网络资源中寻找。

需要注意的是,由于时钟脉冲计数器属于电子技术领域的内容,需要具备一定的电子技术基础才能进行有效的学习和应用。

除了八进制时钟脉冲计数器,还有其他类型的时钟脉冲计数器,如十进制计数器和二进制计数器等。

不同类型的计数器适用于不同的场合,可以根据具体需求进行选择和应用。

此外,随着电子技术的不断发展,时钟脉冲计数器的应用范围也越来越广泛,包括计算机、无线通信、嵌入式系统等方面,有着重要的应用价值。

到此,以上就是小编对于verilog 计数器的问题就介绍到这了,希望介绍的4点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏