大家好,今天小编关注到一个比较有意思的话题,就是关于verilog为什么要用计数器的问题,于是小编就整理了3个相关介绍的解答,让我们一起看看吧。

7进制加减可控计数器74160quartus?

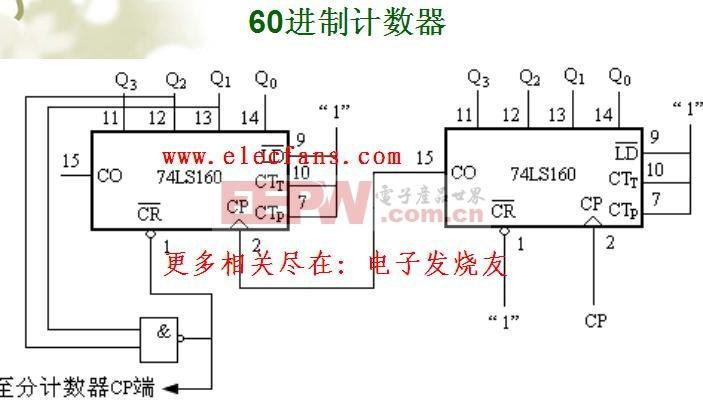

SN74160 是一种 BCD 十进制计数器,它只能够进行十进制的计数,而不能直接进行七进制运算。因此,如果您需要实现 7 进制的加减法计数器,您需要先将 7 进制的数字转化为二进制进行计算,然后再将计算结果转化为 7 进制输出。

对于 Quartus,您可以使用 Altera 的 Quartus II 软件进行设计。针对 SN74160,Quartus II 中并没有现成的器件库,您需要手动进行器件的设计与仿真。在设计七进制加减可控计数器时,您可以参考以下步骤:

1. 设计一个 BCD 计数器,使用 SN74160 的逻辑模型。

2. 将 BCD 计数器的输出转换为 二进制 输出。

3. 设计一个可控加减器,可通过控制端控制加减操作。

回答如下:对于7进制加减可控计数器74160,其功能为可以在两种模式下计数:二进制或BCD码。同时,可以实现加减计数,以及可控制计数范围。

在Quartus中,可以通过以下步骤实现设计:

1. 打开Quartus软件,创建一个新的工程。

2. 在工程中创建一个新的文件,选择Verilog作为设计语言。

3. 在Verilog文件中定义输入和输出端口,以及内部的寄存器和计数器。

4. 实现计数器的逻辑功能,包括加减计数、可控制计数范围等。

5. 编译并生成设计文件,进行仿真和验证。

具体实现细节可参考74160的数据手册和Quartus软件的相关文档。

verilog hdl 频率计为什么显示的数据不稳定?

Verilog HDL中的频率计可能显示不稳定的数据是由于以下原因之一:

1)时钟信号不稳定,可能存在时钟抖动或噪声导致计数不准确;

2)设计中存在时序问题,导致计数器无法正确地进行计数;

3)计数器的设计不合理,可能存在竞争条件或冲突,导致计数不准确;

4)测试环境不稳定,可能存在干扰或噪声导致计数器输出不稳定。要解决这个问题,可以检查时钟源的稳定性,优化设计以避免时序问题,重新设计计数器以解决竞争条件,并确保测试环境的稳定性。

有干扰输入 FPGA速率快,所以可以捕捉到很小的波形 你可以考虑在低频的时候让FPGA工作慢一点

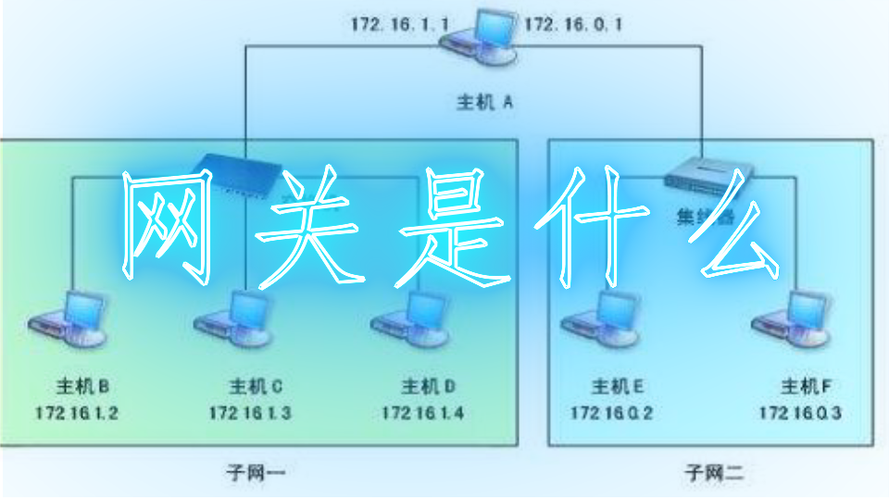

如何开通数电?

要开通数电,首先需要学习数字电路的基础知识,包括逻辑门、布尔代数、时序电路等。可以通过自学或参加相关课程来掌握这些知识。

其次,需要熟悉常用的数字电路元件,如与门、或门、非门等,并学会使用它们进行逻辑设计。

还需要学习数字电路的设计方法和工具,如VHDL或Verilog语言,以及常用的电路仿真软件。

最后,通过实践和项目经验来提升自己的数电能力,例如设计和实现简单的计数器、加法器等电路。不断学习和实践将帮助你开通数电,并在数字电路领域取得进一步的成就。

到此,以上就是小编对于verilog计数器原理的问题就介绍到这了,希望介绍的3点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏