大家好,今天小编关注到一个比较有意思的话题,就是关于ddr数据线为什么串电阻的问题,于是小编就整理了2个相关介绍的解答,让我们一起看看吧。

ddr端接电阻的作用?

ddt端接店主为的是能够确保整个电路的电流能够顺畅的运行。

串行端接电阻多用作源端阻抗匹配,故一般放置靠近信号源所在端,如cpu的clk。

上拉电阻是用来解决总线驱动能力不足时提供电流的,一般说法是拉电流 ...

端接技术主要分为三种端接方式:串行端接,并行端接,差分端接

关于三种端接电阻的位置:

串行端接电阻多用作源端阻抗匹配,故一般放置靠近信号源所在端,如cpu的clk。

并行端接电阻多用于负载端阻抗匹配,故一般放置靠近负载一侧。

其中差分端接属于并行短接,个人观点。

串行端接电阻记作Rs,并行端接电阻记作Rt。

ddr的pcb走线要求?

DDR(Double Data Rate)是一种常用的动态随机存取存储器(DRAM)类型,其PCB(Printed Circuit Board,印刷电路板)的走线设计对DDR性能至关重要。以下是DDR PCB走线的一些常见要求和考虑因素:

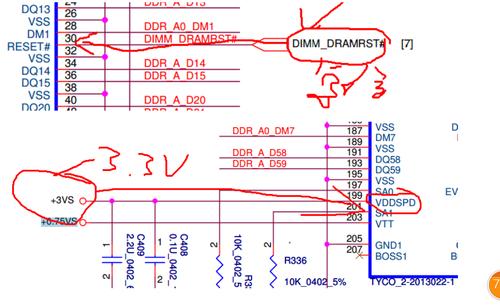

1. 长度匹配:DDR接口需要严格的长度匹配,以确保数据和时钟信号的到达时间一致。因此,需要对信号线在PCB上进行控制,确保不同信号的传输时间尽量相等。

2. 终端电阻:DDR接口需要在数据线上使用终端电阻来匹配传输线的阻抗,从而减少传输线的反射和时钟抖动。常用的DDR终端电阻阻值为50欧姆。

3. 差分对走线:在DDR的数据传输中,常常使用差分对进行信号传输。在PCB走线设计中,需要将差分对走线保持匹配,以保持信号的相位和幅度一致。

4. 信号层分离和自吸收:DDR的PCB设计通常采用多层结构,使用不同的信号层来分离和隔离不同的信号,减少相互之间的干扰。此外,需要避免信号线和供电/接地平面之间的交叉,以减少自吸收和信号串扰。

DDR(Double Data Rate)的PCB走线要求如下:

1. 对称性布局:DDR的数据线要求有相同的长度和形状,以保持信号的同步传输。因此,DDR的PCB走线需要对称布局,确保数据线和地址线的长度相等且线宽一致。

2. 不交叉走线:DDR的数据线和地址线不应该交叉走线,以避免信号的串扰和干扰。因此,在PCB设计中,需要根据布局要求将数据线和地址线分开布置,并确保它们没有交叉。

3. 地线和电源线的布置:DDR的PCB走线需要合理布置地线和电源线,以确保信号的良好接地和供电。地线和电源线应该靠近数据和地址线,最小化地线和电源线与其他信号线之间的距离,减少信号串扰和干扰。

4. 一对一匹配:DDR的PCB走线需要将数据线和地址线进行一对一匹配。这意味着每根数据线都需要相应的地址线来配对,以保持信号同步和稳定传输。

5. 控制和时钟线的布置:DDR的PCB走线还需要合理布置控制线和时钟线,以确保它们与数据线和地址线之间的相互作用最小化。控制线和时钟线应该靠近需要控制或同步的数据和地址线,以减少信号的传播延迟和时钟抖动。

总之,DDR的PCB走线需要注重对称性,不交叉走线,并合理布置地线、电源线、控制线和时钟线,以保证信号的稳定和良好的传输性能。

到此,以上就是小编对于ddr数据线为什么串电阻呢的问题就介绍到这了,希望介绍的2点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏